原标题:1nm以后的晶体管选择:CFET? 来源:半导体行业观察

在VLSI 2020上,IMEC发表了有关单片CFET的有趣论文,我有机会采访了其中一位作者Airoura Hiroaki。在业界众所周知,FinFET(FF)即将达到其定标寿命。三星已经宣布,他们将在3nm的时候转向水平纳米片(Horizontal Nanosheets :HNS)。台积电(TSMC)保持3nm的FF,但预计将转移到2nm的新架构。

假设英特尔当时仍在追求自己的技术,则预计英特尔将保留7nm的FF,然后再迁移至5nm的HNS。

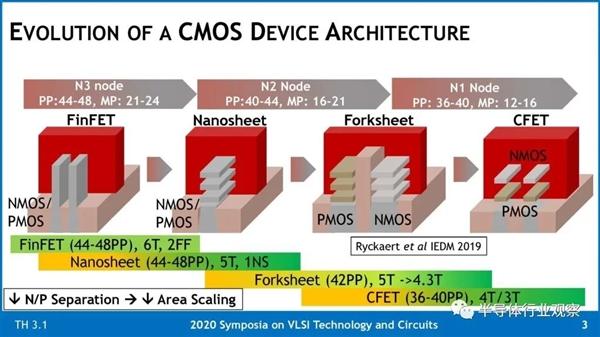

该行业最可能的路线图是从FF到带有或不带有Forksheets的HNS,然后过渡到CFET(Complimentary FETs),请参见图1。

ImecCMOS路线图。

从以上技术蓝图来看,28纳米使用了High-K/Metal Gate,16纳米---14纳米导入了FinFET,7纳米---5纳米采用了EUV曝光设备,此外,还将Co应用于Middle of Line(MOL)上。

MOL是一种将晶体管(FOEL)与多层配线(BEOL)连接在一起的孔(Via),虽然imec使用了Co,还有其他选择项如Mo、Ru等。

此外,4纳米---3纳米中采用了具有Nanosheet结构的晶体管。

此次的VLSI座谈会上,有关7纳米、5纳米、3纳米的文章发布得比较多,然而,笔者却发现将Gate All Around(GAA)的Nanosheet结构应用在这些节点上的情况是全球共通的认知。

同时从技术蓝图看,在2纳米中,使用搭载了Buried Power Rail(BPR,在晶体管下埋入电源线的构造)的Forksheet晶体管;在1纳米中,将会使用采用了BPR的Complementary FET(CFET)。

imec在其内部达成了以下共识:3纳米之前采用Nanosheet、2纳米采用Forksheet、1纳米采用CFET。

也就是说,在此次VLSI座谈会上,imec也是基于以上技术蓝图而做的发表。从上图可以清晰地看出FinFET、Nanosheet、Forksheet、CFET的结构变化。

从FinFET到CFET,通过将Contact Poly Pitch(PP)做到最小、分离nMOS和pMOS,以达到缩小SRAM面积的效果。

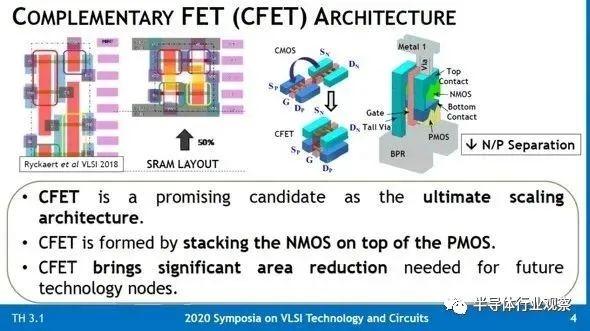

Forksheet 和CFET通过堆叠nFET和pFET器件的CFET改善n到p的间距来缩小尺寸,见图2。

CFET结构在当前的工作中,已经开发了“单片”(monolithic) CFET,方法是将单独的硅片用于nFET和pFET,然后将它们粘合在一起,而按照顺序(sequential),CFET则会将两种类型的FET都制造在同一硅片上。

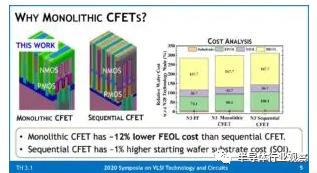

Imec声称单片技术比顺序技术便宜,而顺序技术要求SOI会增加衬底成本1%,见图3。

单片CFET的成本优势在1纳米中,IMEC采用了将nMOS和pMOS纵向排列的CFET(如下图8),虽然CFET的工艺流程非常复杂,但毫无疑问,极大地缩小了CMOS、SRAM的面积,达到了集成化。

问题是---是否做到了人们所期待的晶体管的特性,这是未来研发的关键。

我发现起始晶圆成本高出约1%,这有两个原因,一是,我不相信顺序CFET需要SOI,二是,SOI比标准晶圆贵了约1%。整体方法还将需要两个起始晶圆,而不仅仅是一个。

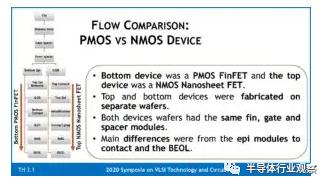

我认为这种成本分析需要更多的调查。在单片方法中,nFET和pFET在分离的晶圆上制造,从而可以针对该器件优化每个器件的制造流程。每个晶片的处理流程如图4所示。

图4.单片CFET的工艺流程。

随着我们朝N3方向发展,n到p的分离减少了寄生效应并提高了性能。同样,通过从FF移至GAA)可以在所有四个侧面而不是三个侧面上提供一个栅极,从而改善了静电控制。

这项工作中制造的单片CFET为下一代器件提供了顺序CFET的替代方案,需要进一步研究。